ARTESYN LGA50D SERIES

Non Isolated DCDC Converter

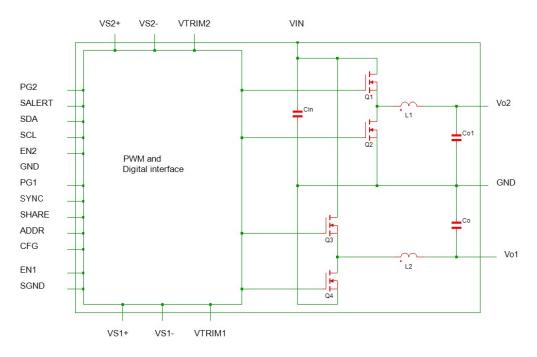

# **PRODUCT DESCRIPTION**

The LGA50D power supply features a 7.5 to 14 Vdc input voltage range and a 120W output power.

The LGA50D is a new design of high performance DC-DC converter. LGA50D has 2 phase design. It offers a total 120W output with just dimensions of  $1.0^{\circ}x0.5^{\circ}x$  0.48". State-of-the-art circuit topology provides a very high efficiency up to 95.5% which allows an operating temperature range of -40 °C to +85 °C.

Further features include remote On/Off, variable output voltage as well as over-current protection, over-voltage protection, and over-temperature protection.

# **SPECIAL FEATURES**

- 2 phase design

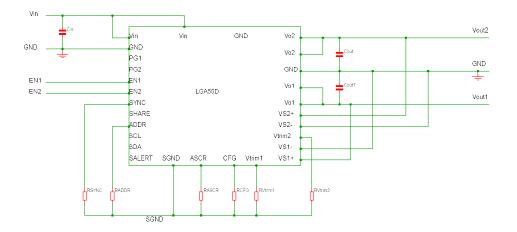

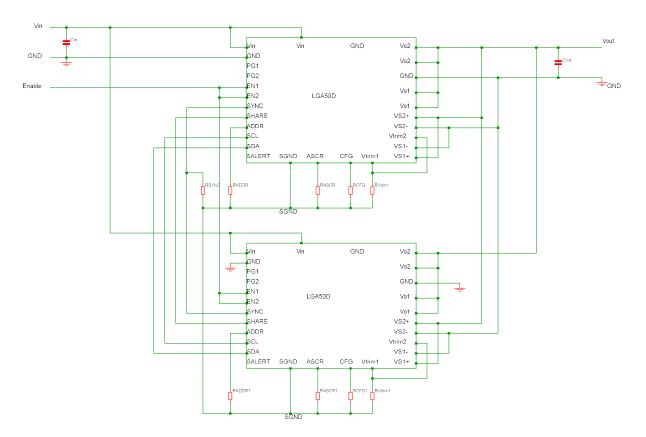

- Dual or single output configuration possible

- High efficiency up to 95.5%

- Small size 1" x 0.5" x 0.48" (LxWxH) (LGA50D-01DADJJ)

- Small size 1" x 0.5" x 0.42" (LxWxH) (LGA50D-01DADJSBJ)

- PMBus<sup>™</sup> supporting

- No minimum load requirement

- Wide operating temperature range

- Exceptional power density

- Automatic loop compensation

- Excellent transient response

- Analog or Digital control

- Tape and reel packaging

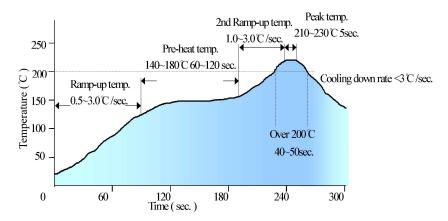

- Reflow compatible

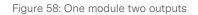

- Possible to stack up to 8 phases for 200A

- I-mon and T-mon supported

- Two variants supported

- Block pin termination

- Solder bump termination

- IPC9592B compliant @ V<sub>IN</sub> = 13.2Vdc

# SAFETY

- Designed to meet EN60950-1 and EN62368-1

- UKCA Mark

### AT A GLANCE

### **Total Power**

120 Watts

### **Total Current**

50 A (Single)

25 A (Dual)

### **Output Voltage**

0.6 to 5 Vdc

### # of Outputs

Dual or Single

### LGA50D Series

# **MODEL NUMBERS**

| Standard         | Input Voltage | Input Voltage Output Voltage |    | Maximum Load |

|------------------|---------------|------------------------------|----|--------------|

| LGA50D-01DADJJ   | 7.5-14Vdc     | 0.6-5.0Vdc                   | 0A | 50A          |

| LGA50D-01DADJSBJ | 7.5-14Vdc     | 0.6-5.0Vdc                   | 0A | 50A          |

### **Order Information**

| LGA | 50 | D | - | 01 | D | ADJ | SB |   | J |

|-----|----|---|---|----|---|-----|----|---|---|

| 1)  | 2  | 3 |   | 4  | 5 | 6   | 7  | 8 | 9 |

| 1   | Model series        | LGA: Series Name                                                 |  |  |  |

|-----|---------------------|------------------------------------------------------------------|--|--|--|

| 2   | Output current      | 50: Rated Output Current = 50A                                   |  |  |  |

| 3   | Control             | D: Digital Control POL                                           |  |  |  |

| (4) | Input Voltage Range | 01: 7.5 to 14Vdc                                                 |  |  |  |

| 5   | Number of Outputs   | D: Dual Output                                                   |  |  |  |

| 6   | Output type         | ADJ: Adjustable Output                                           |  |  |  |

| 7   | Mechanical Options  | Blank: Block Pin termination type<br>SB: Solder bump termination |  |  |  |

| 8   | Other Options       | Blank: Latching mode during protection                           |  |  |  |

| 9   | Rohs Compliance     | J:Pb free (Rohs 6/6 compliant)                                   |  |  |  |

### **Absolute Maximum Ratings**

Stress in Stress in excess of those listed in the "Absolute Maximum Ratings" may cause permanent damage to the power supply. These are stress ratings only and functional operation of the unit is not implied at these or any other conditions above those given in the operational sections of this TRN. Exposure to any absolute maximum rated condition for extended periods may adversely affect the power supply's reliability.

| Table 1. Absolute Maximum Ratings                                                                        |            |                  |      |     |      |      |

|----------------------------------------------------------------------------------------------------------|------------|------------------|------|-----|------|------|

| Parameter                                                                                                | Model      | Symbol           | Min  | Тур | Max  | Unit |

| Input Voltage (DC continuous operation)                                                                  | All models | V <sub>IN</sub>  | -    | -   | 15   | V    |

| Operating Ambient Temperature <sup>1</sup>                                                               | All models | T <sub>A</sub>   | -40  | -   | +85  | °C   |

| Storage Temperature                                                                                      | All models | T <sub>STG</sub> | -40  | -   | +125 | °C   |

| Output Voltage                                                                                           | All models | V <sub>OUT</sub> | 0.6  | -   | 5.0  | V    |

| Logic I/O Voltage<br>SHARE,EN1, EN2, PG1, PG2, SALRT, SCL, SDA,<br>SYNC, VSET0, VSET1,CFG, ADDR, ASCRCFG | All models |                  | -0.3 | -   | 6.0  | V    |

| Analog Input Voltages<br>VS1+, VS1-, VS2+, VS2-                                                          | All models |                  | -0.3 | -   | 6.5  | V    |

Note 1 - At low temperatures, (at < -20°C), the accuracy of PMBus<sup>TM</sup> monitored parameters will be adversely affected. At high temperatures, please refer to "Thermal Derating" section.

### **Input Specifications**

| Parameter                                                            | Condition <sup>1</sup>                                                                                          | Symbol              | Min                                  | Nom                                  | Max          | Unit             |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------|--------------------------------------|--------------|------------------|

| Operating Input Voltage, DC <sup>2</sup>                             | $0.6 \le V_0 \le 3.3 V$<br>$3.3 < V_0 \le 5V$                                                                   | V <sub>IN</sub>     | 7.5<br>10                            |                                      | 14<br>14     | V<br>V           |

| Maximum Input Current                                                | V <sub>IN</sub> =7.5Vdc                                                                                         | I <sub>IN,max</sub> | -                                    | -                                    | 20           | А                |

| Standby Input Current<br>(V <sub>0</sub> = Off, I <sub>0</sub> = 0A) | f <sub>sw</sub> =571KHz<br>f <sub>sw</sub> =800KHz                                                              | I <sub>IN</sub>     |                                      | 45<br>50                             | 50<br>55     | mA<br>mA         |

| Standby Input Power $(V_0 = Off, I_0 = 0A)$                          | f <sub>SW</sub> =571KHz<br>f <sub>SW</sub> =800KHz                                                              | P <sub>IN</sub>     |                                      | 0.54<br>0.60                         | 0.60<br>0.66 | W<br>W           |

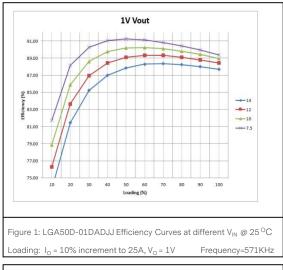

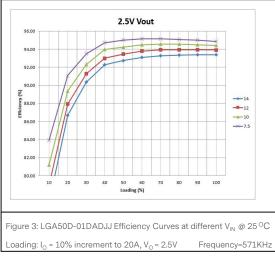

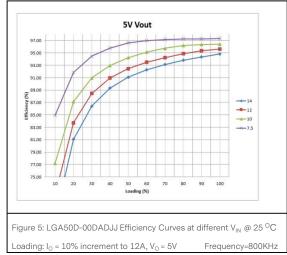

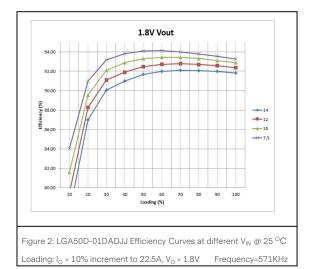

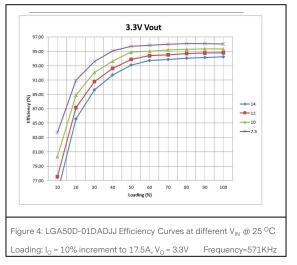

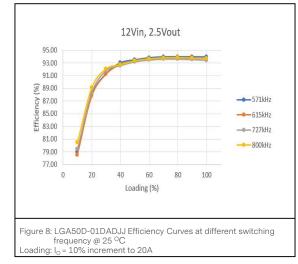

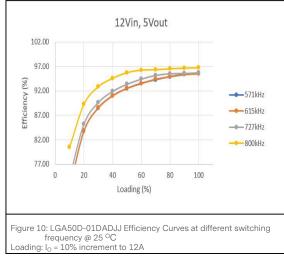

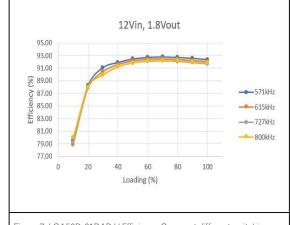

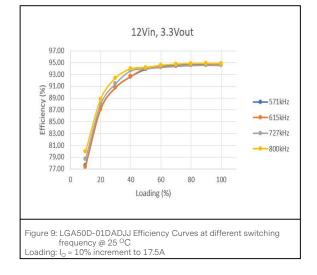

| Efficiency at 12V & 25 <sup>o</sup> C                                | 1.0V at 50A &571KHz<br>1.8V at 45A &571KHz<br>2.5V at 40A &571KHz<br>3.3V at 35A &571KHz<br>5.0V at 24A &800KHz |                     | 87.5<br>91.0<br>92.5<br>93.5<br>94.0 | 88.2<br>92.2<br>93.7<br>94.6<br>95.5 |              | %<br>%<br>%<br>% |

| Input Capacitor (Internal)                                           |                                                                                                                 |                     | -                                    | 28.2                                 | -            | uF               |

| Input Capacitor (External required) <sup>3</sup>                     |                                                                                                                 |                     | -                                    | 88                                   | -            | uF               |

| Input Voltage UVLO Threshold Range <sup>4</sup>                      | Falling                                                                                                         |                     | 6.5                                  | 6.9                                  | -            | V                |

| Input Voltage UVLO Threshold Range <sup>4</sup>                      | Rising                                                                                                          |                     | -                                    | 7.2                                  | 7.5          | V                |

| Logic Input/Output Characteristics                                   |                                                                                                                 |                     |                                      |                                      |              |                  |

| Logic Input Low, VIL                                                 |                                                                                                                 |                     | -                                    | -                                    | 0.8          | V                |

| Logic Input High, VIH                                                |                                                                                                                 |                     | 2                                    | -                                    | -            | V                |

| Logic Output Low, VOL                                                | 2mA sinking                                                                                                     |                     | -                                    | -                                    | 0.5          | V                |

| Logic Output High, VOH                                               | 2mA sourcing                                                                                                    |                     | 2.25                                 | -                                    | -            | V                |

| Logic Input Leakage Current                                          |                                                                                                                 |                     | -100                                 | -                                    | 100          | nA               |

Note 1 - Typical values given at V<sub>IN</sub>=12V, switching frequency = 571KHz for 0.6V ≤ V<sub>0</sub> ≤ 3.3V and switching frequency = 800kHz for 3.3V < V<sub>0</sub> ≤ 5V, 25<sup>o</sup>C , unless otherwise specified under conditions.

Note 2 - To maintain compliance to IPC9592B, input voltage must be kept at <13.2V. For 5V output working below 10V V<sub>IN</sub> please contact Advanced Energy

to support.

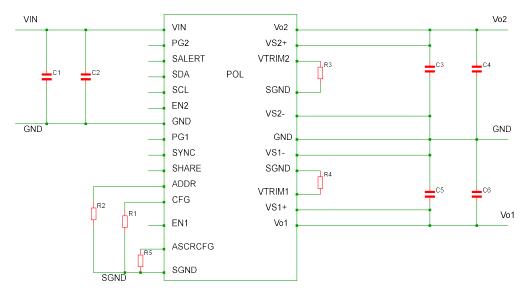

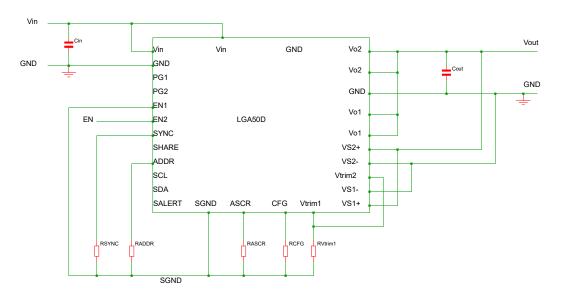

Note 3 - Minimum: 4 x 22uF/16V 0805 ceramic cap ( C2012X6S1C226M125AC or equivalent).

Recommended: 1x120uF/16V polymer caps (APXS160ARA121MH 70G or equivalent) + 4 x 22uF/16V ceramic cap. Note 4 - For 5V<sub>OUT</sub>, it is recommend to use PMBus<sup>™</sup> to set UVLO (Falling) to 8.9V and UVLO (Rising) to 9.2V. However, there is no problem for operation without setting the recommended 5V<sub>OUT</sub> UVLO.

## **Output Specifications**

| Parameter                                                                | Condition                                                                                                                                                                                                              | Symbol                                                                                | Min                   | Nom                   | Max                                          | Unit                                      |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------------------------------|-------------------------------------------|

| Output Voltage                                                           | V <sub>IN</sub> = 7.5V to 14V<br>V <sub>IN</sub> = 10V to 14V                                                                                                                                                          | V <sub>0</sub> 1, V <sub>0</sub> 2<br>V <sub>0</sub> 1, V <sub>0</sub> 2 <sup>2</sup> | 0.6<br>0.6            | -                     | 3.3<br>5.0                                   | Vdc<br>Vdc                                |

| Output Current<br>(Independent Output 1 and 2)                           | $V_{O}1 \text{ or } V_{O}2 = 0.6V$ $V_{O}1 \text{ or } V_{O}2 = 1.0V$ $V_{O}1 \text{ or } V_{O}2 = 1.8V$ $V_{O}1 \text{ or } V_{O}2 = 2.5V$ $V_{O}1 \text{ or } V_{O}2 = 3.3V$ $V_{O}1 \text{ or } V_{O}2 = 5.0V$      | I <sub>0</sub> 1<br>I <sub>0</sub> 2                                                  | 0<br>0<br>0<br>0<br>0 | -<br>-<br>-<br>-      | 25.0<br>25.0<br>22.5<br>20.0<br>17.5<br>12.0 | A<br>A<br>A<br>A<br>A                     |

| Combined output 1 and 2                                                  | $\begin{array}{l} V_{\rm O} = 0.6V \\ V_{\rm O} = 1.0V \\ V_{\rm O} = 1.8V \\ V_{\rm O} = 2.5V \\ V_{\rm O} = 3.3V \\ V_{\rm O} = 5.0V \end{array}$                                                                    | Ι <sub>ο</sub>                                                                        | 0<br>0<br>0<br>0<br>0 | -<br>-<br>-<br>-<br>- | 50<br>50<br>45<br>40<br>35<br>24             | A<br>A<br>A<br>A<br>A                     |

| Output Power                                                             | All                                                                                                                                                                                                                    | Po                                                                                    | -                     | -                     | 120                                          | W                                         |

| Output Set-point Accuracy <sup>1</sup>                                   | Set by PMBus™ or 1%<br>trim resistors                                                                                                                                                                                  |                                                                                       | -1.2                  | -                     | +1.2                                         | %                                         |

| Output Voltage Set-point Resolution                                      | Set by PMBus™<br>command                                                                                                                                                                                               | V <sub>o</sub>                                                                        | -0.05                 | -                     | +0.05                                        | %                                         |

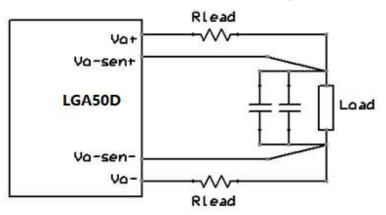

| Output Voltage Positive Sensing Bias Current                             | VS [0,1] + = 4V (negative = sinking)                                                                                                                                                                                   |                                                                                       | -100                  | -                     | 100                                          | μΑ                                        |

| Output Voltage Negative Sensing Bias Current                             | VS [0,1] - = 0V                                                                                                                                                                                                        |                                                                                       | -                     | 20                    | -                                            | μΑ                                        |

| Line Regulation                                                          | 0.6V≤V <sub>0</sub> ≤1.0V<br>1.0V < V <sub>0</sub> ≤5.0V                                                                                                                                                               |                                                                                       | -                     | 2<br>0.2              | 10<br>1                                      | mV<br>%                                   |

| Load Regulation                                                          | $0.6V \le V_{O} \le 1.0V$<br>$1.0V < V_{O} \le 5.0V$                                                                                                                                                                   |                                                                                       | -                     | 5<br>0.5              | 10<br>1                                      | mV<br>%                                   |

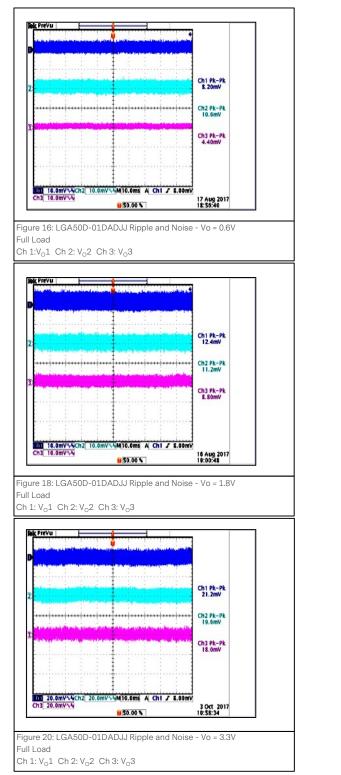

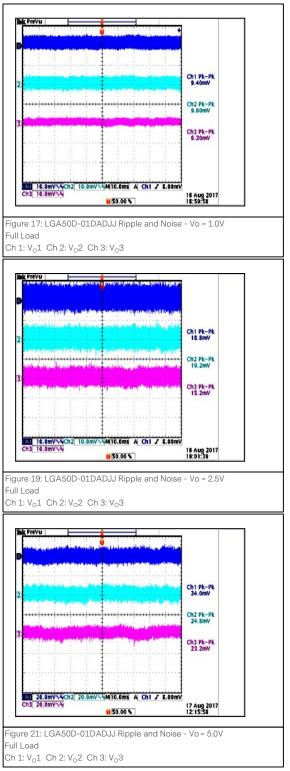

| Ripple and Noise (with recommended caps)<br>Single Output                | $0.6V \le V_{O} \le 1.0V$<br>$1.0V < V_{O} \le 5.0V$                                                                                                                                                                   |                                                                                       | -                     | 10<br>1               | 20<br>2                                      | mV <sub>pk-pk</sub><br>% <sub>pk-pk</sub> |

| Ripple and Noise (with recommended caps) Dual outputs( $V_01$ , $V_02$ ) | 0.6V≤V <sub>0</sub> ≤1.0V<br>1.0V < V <sub>0</sub> ≤5.0V                                                                                                                                                               |                                                                                       | -                     | 10<br>1               | 20<br>1                                      | mV <sub>pk-pk</sub><br>% <sub>pk-pk</sub> |

| Transient Response Deviation<br>(Independent Output 1 and 2)             | $\begin{array}{c} 50\% \text{ of Io} \\ \text{step Ioad, slew rate} \\ 1 \text{A/us} \\ 0.6 \text{V}{\leq} \text{V}_{\text{O}}{\leq} 1.0 \text{V} \\ 1.0 \text{V} < \text{V}_{\text{O}} \leq 5.0 \text{V} \end{array}$ |                                                                                       |                       | 50<br>3               | 60<br>4                                      | mV <sub>pk-pk</sub><br>% <sub>pk-pk</sub> |

| Transient Response Deviation<br>(Combined output 1 and 2)                | 50% of Io<br>step Ioad, slew rate<br>1A/us<br>0.6V≤V <sub>O</sub> ≤1.0V<br>1.0V < V <sub>O</sub> ≤5.0V                                                                                                                 |                                                                                       | -                     | 30<br>3               | 40<br>4                                      | mV <sub>pk-pk</sub><br>% <sub>pk-pk</sub> |

| Output Capacitor per Output (external                                    | Dual outputs                                                                                                                                                                                                           | Co                                                                                    | -                     | 2200                  | -                                            | uF                                        |

| minimum) <sup>3</sup>                                                    | Single output                                                                                                                                                                                                          | Co                                                                                    | -                     | 2400                  | -                                            | uF                                        |

### **Output Specifications**

| Table 3. Output Specifications con't                                 |                                                                                         |        |        |        |           |                 |  |  |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------|--------|--------|-----------|-----------------|--|--|--|--|--|

| Parameter                                                            | Condition                                                                               | Symbol | Min    | Nom    | Max       | Unit            |  |  |  |  |  |

| Quitables Frequency5                                                 | $0.6V \le V_{O} \le 3.3V$                                                               |        | 571    | 571    | 800       | KHz             |  |  |  |  |  |

| Switching Frequency <sup>5</sup>                                     | $3.3V < V_{O} \le 5V$                                                                   |        | -      | 800    | -         | KHz             |  |  |  |  |  |

| PMBus <sup>™</sup> Clock Frequency <sup>4</sup>                      |                                                                                         |        | 100    | -      | 400       | KHz             |  |  |  |  |  |

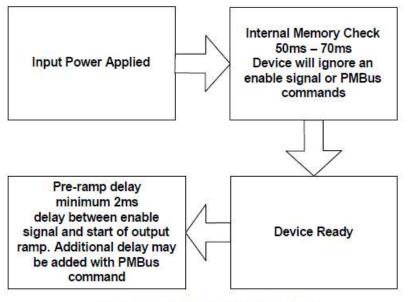

| Ton Delay/Toff Delay                                                 |                                                                                         |        | -      | 5      | -         | mS              |  |  |  |  |  |

| Ton Delay/Toff Delay Range                                           | Set by PMBus™<br>command                                                                |        | 2      | -      | 5000      | mS              |  |  |  |  |  |

| Ramp Delay/Toff Delay Accuracy                                       | Turn on,Turn off delay                                                                  |        | 0      | -      | 2         | mS              |  |  |  |  |  |

| Ton Ramp/Toff Ramp Duration                                          | Default (2 phase or 2<br>channel only)                                                  |        | -      | 5      | 10        | mS              |  |  |  |  |  |

| Power Good Vo Threshold                                              |                                                                                         |        | 85     | 90     | 95        | %               |  |  |  |  |  |

| Power Good Vo Hysteresis                                             |                                                                                         |        | -      | 5      | 10        | %               |  |  |  |  |  |

| Power-good Delay<br>Applies to turn-on only (Low to High transition) | Factory Default<br>Set using PMBus™                                                     |        | -<br>0 | 1<br>- | 2<br>5000 | mS<br>mS        |  |  |  |  |  |

| Power Good Low Voltage                                               | V <sub>IN</sub> from 0-14V                                                              |        | -      | -      | 0.5       | V               |  |  |  |  |  |

| СМТВР                                                                | Calculated according to<br>Bellcore or Telcordia TR-<br>NTW-000332 at 40°C<br>full-load |        | 50     | -      | -         | MHours          |  |  |  |  |  |

| Over Voltage Protection                                              | All                                                                                     |        | -      | 110    | -         | %V <sub>o</sub> |  |  |  |  |  |

| Over Current Protection <sup>6</sup>                                 | I <sub>0</sub> 1, I <sub>0</sub> 2                                                      |        | -      | -      | 35        | А               |  |  |  |  |  |

| Over Temperature Protection                                          | All                                                                                     |        | -      | 110    | 125       | °C              |  |  |  |  |  |

Note 1 -  $V_0$  measured at the termination of the VSx+ and VSx- sense points across line, load, temperature variation. Note 2 - Vo1 and Vo2 are the outputs of dual output module. Note 3 - Dual mode (2 outputs): 2 x 680uF/6.3V Polymer Tan caps (T530X687M006ATE010 or equivalent)

+ 8 x 100uF/6.3V X6S 1210 ceramic caps (GRM32EC80J107ME20L or equivalent)

+ 4x10uF/16V X6S 0603 ceramic caps (GRM188C81C106MA73 or equivalent)

Single mode (1 output): 2 x 680uF/6.3V Polymer Tan caps (T530X687M006ATE010 or equivalent)

+ 10 x 100uF/6.3V X6S 1210 ceramic caps (GRM32EC80J107ME20L or equivalent)

+ 4x10uF/16V X6S 0603 ceramic caps (GRM188C81C106MA73 or equivalent)

Note 4 - For operation PMBus<sup>TM</sup> clock frequency at 400kHz, see PMBus<sup>TM</sup> Power System Management Protocol Specification for timing parameter limits. Note 5 - For dual outputs condition, the switching frequency of both outputs must be the same. Also, must use the higher switching frequency between the

2 outputs. For example, if Vout1= 0.6V and Vout2= 5V, the switching frequency for both outputs must be set to 800kHz. Note 6 - The OCP set point applies per phase. The total OCP current value will be twice of Io1 in single mode. Please refer to Table 10 for OCP setting.

### LGA50D Series

# **ELECTRICAL SPECIFICATIONS**

#### LGA50D-01DADJJ Performance Curves

Advanced Energy

### LGA50D Series

### **ELECTRICAL SPECIFICATIONS**

#### LGA50D-01DADJJ Performance Curves

Figure 7: LGA50D-01DADJJ Efficiency Curves at different switching frequency @ 25  $^{\rm O}{\rm C}$  Loading: I<sub>o</sub> = 10% increment to 22.5A

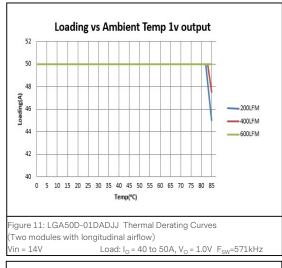

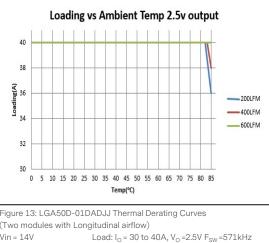

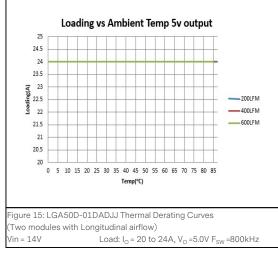

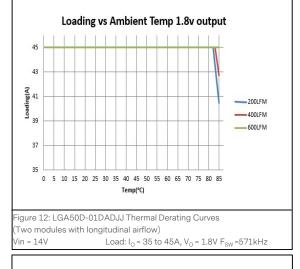

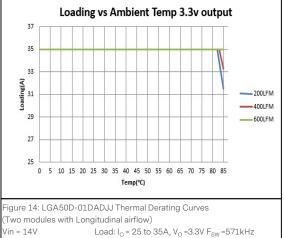

### LGA50D-01DADJJ Performance Curves (Thermal Derating)

Note: One module temperature is much better than two modules.

### LGA50D-01DADJJ Performance Curves (Ripple and Noise)

Note:  $V_{\rm O}{\rm 1}$  and  $V_{\rm O}{\rm 2}$  are the outputs of dual output module,  $V_{\rm O}{\rm 3}$  is the output of single output module.

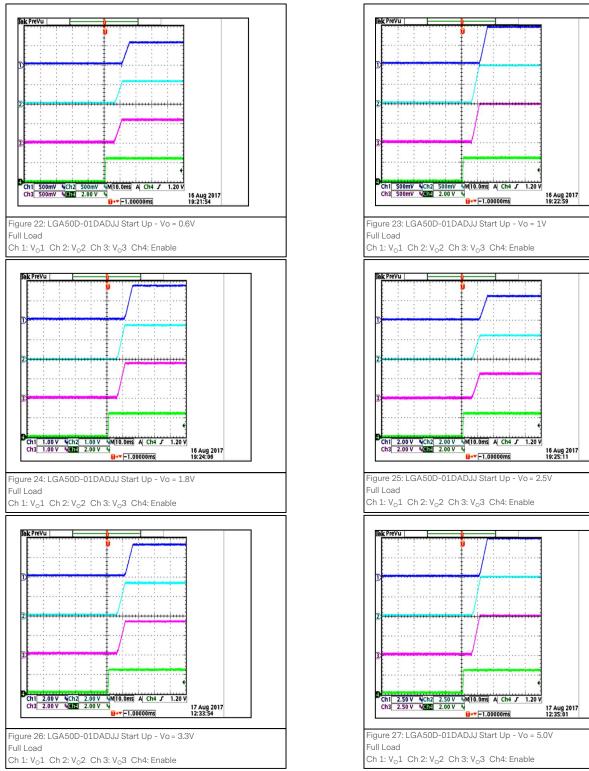

### LGA50D-01DADJJ Performance Curves (Start Up)

Note:  $V_{\rm O}{\rm 1}$  and  $V_{\rm O}{\rm 2}$  are the outputs of dual output module,  $V_{\rm O}{\rm 3}$  is the output of single output module.

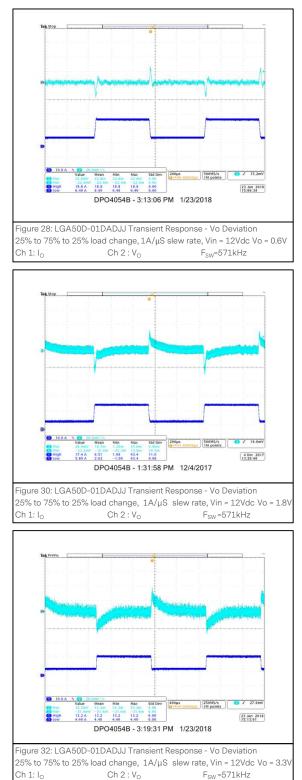

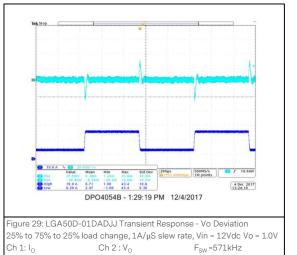

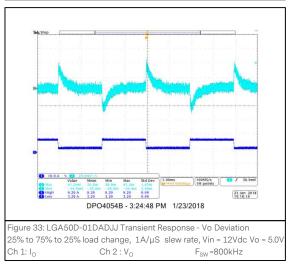

### LGA50D-01DADJJ Performance Curves (Slow Dynamic Load Response – 2 phase 2 output)

$\begin{array}{l} \mbox{Figure 31: LGA50D-01DADJJ Transient Response - Vo Deviation} \\ \mbox{25\% to 75\% to 25\% load change, 1A/\muS slew rate, Vin = 12Vdc Vo = 2.5V} \\ \mbox{Ch 1: I}_0 & \mbox{Ch 2: V}_0 & \mbox{F}_{SW} = 571 \mbox{HHz} \\ \end{array}$

Advanced Energy

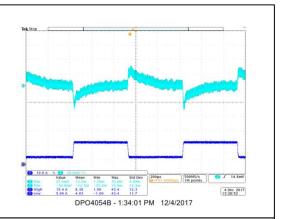

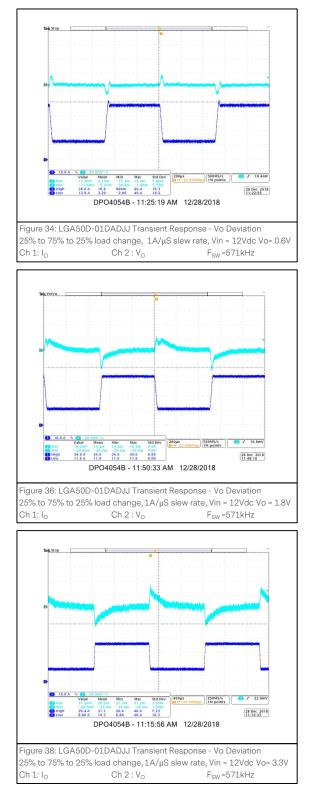

### LGA50D-01DADJJ Performance Curves (Slow Dynamic Load Response - 2 phase 1 output)

Figure 39: LGA50D-01DADJJ Transient Response - Vo Deviation25% to 75% to 25% load change,  $1A/\mu S$  slew rate, Vin = 12Vdc Vo = 5.0VCh 1: I<sub>0</sub>Ch 2 : V<sub>0</sub>F<sub>SW</sub>=800kHz

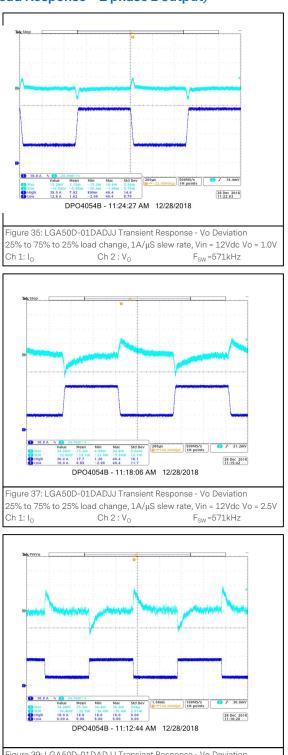

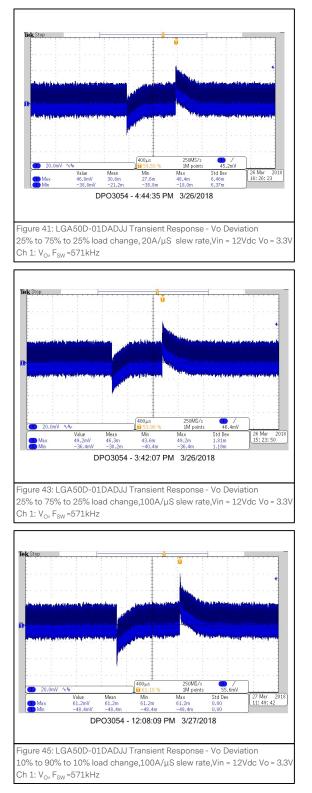

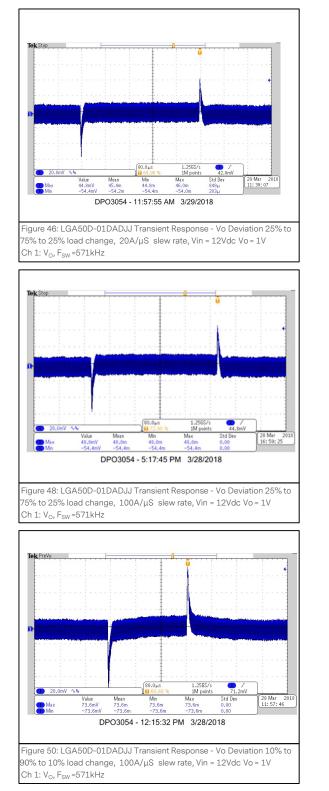

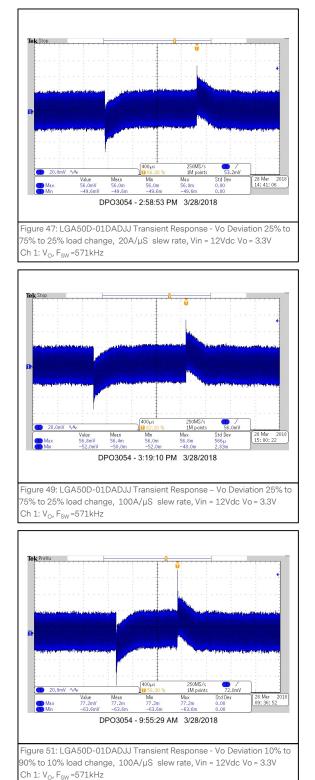

### LGA50D-01DADJJ Performance Curves (Fast Dynamic Load Response – 2 phase 2 output)

Advanced Energy

### LGA50D-01DADJJ Performance Curves (Fast Dynamic Load Response – 2 phase 1 output)

Note: Switching frequency: 0.6Vout - 3.3Vout = 571kHz 5Vout = 800kHz

## **PROTECTION SPECIFICATIONS**

#### **Output Overvoltage Protection**

The LGA50D offers an internal output overvoltage protection circuit that can be used to protect sensitive load circuitry from being subjected to a voltage higher than its prescribed limits. A hardware comparator is used to compare the actual output voltage (seen at the VS pin) to a programmable threshold set to 10% higher than the target output voltage (the default setting).

If the VS voltage exceeds this threshold, the PG pin will de-assert and the module will latch.

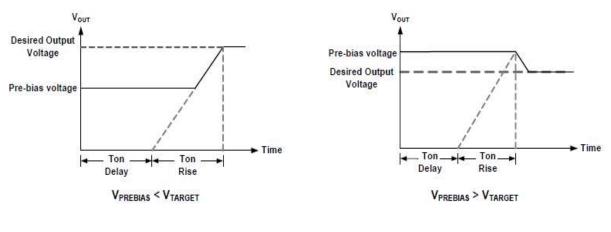

#### **Output Pre-Bias Protection**

The LGA50D provides pre-biased start-up operation in 2 outputs and single module 2 phase operation. Pre-Bias protection is not provided when operating in current sharing 4, 6 or 8 phase configurations. An output pre-bias condition exists when an externally applied voltage is present on a power supply's output before the power supply's control IC is enabled. Certain applications require that the converter not be allowed to sink current during start up if a pre-bias condition exists at the output.

The LGA50D provides pre-bias protection by sampling the output voltage prior to initiating an output ramp.

If a pre-bias voltage lower than the desired output voltage is present after the Ton-delay time the LGA50D starts switching with a duty cycle that matches the pre-bias voltage. This ensures that the ramp-up from the pre-bias voltage is monotonic. The output voltage is then ramped to the desired output voltage at the ramp rate set by the TON\_RISE command.

The resulting output voltage rise time will vary depending on the pre-bias voltage, but the total time elapsed from the end of the Ton-delay time to when the Ton-rise time is complete and the output is at the desired value will match the pre-configured ramp time. See Figure 52 and Figure 53.

If a pre-bias voltage higher than the target voltage exists after the pre-configured Ton-delay time and Ton-rise time have completed, the LGA50D starts switching with a duty cycle that matches the pre-bias voltage. This ensures that the ramp-down from the pre-bias voltage is monotonic. The output voltage is then ramped down to the desired output voltage.

If a pre-bias voltage higher than the overvoltage limit exists, the module will not initiate a turn-on sequence and will stay off with an output OV fault recorded.

Figure 52

Figure 53

## **PROTECTION SPECIFICATIONS**

#### Input Voltage Undervoltage Lock-Out Setting (UVLO)

The input undervoltage lockout (UVLO) prevents the LGA50D from operating when the input falls below a preset threshold, indicating the input supply is out of its specified range. The input voltage undervoltage lock-out threshold can be set between 4.18V and 16V using the VIN\_UV\_FAULT\_LIMIT command. The default UVLO ON and OFF value are 7.2V and 6.9V respectively.

For 5Vout, it is recommended to use PMBus<sup>™</sup> to set UVLO (Falling) to 8.9V and UVLO (Rising) to 9.2V.

However, there is no problem for operation without setting the recommended 5Vout UVLO.

The default response from an undervoltage fault is to shutdown and stay off until the fault has cleared and the module has been disabled and re-enabled.

When controlling the LGA50D exclusively through the PMBus<sup>™</sup> a high voltage setting for UVLO can be used to prevent the LGA50D from being enabled until a lower voltage for UVLO is set using the VIN\_UV\_FAULT\_LIMIT command.

#### **Output Over Current Protection**

The LGA50D can protect the power supply from damage from an overloaded or shorted output. Once the current trigger OCP set point, the unit will latch.

#### **Over Temperature Protection**

The LGA50D provide over temperature protection where the hotspot of the module. There are two over temperature protection sensing point, one is on the controller IC, the other one is on the Mosfet.

Once the module has been disabled due to over temperature fault, the unit will auto recovery once temperature is below typical +110  $^{\circ}$ C of OT\_WARN\_LIMIT.

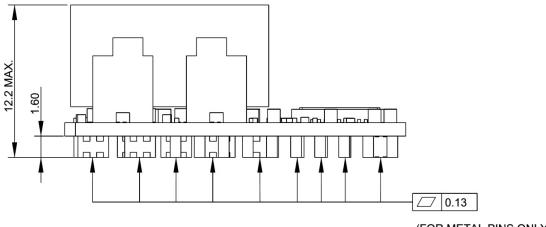

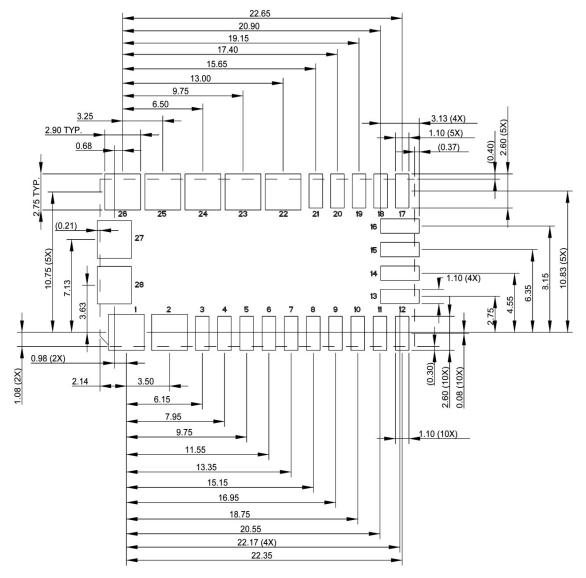

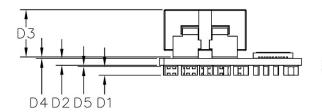

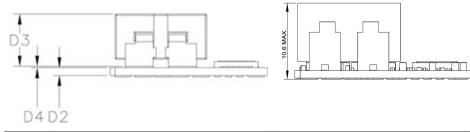

### Mechanical Drawing (Dimensioning and Mounting Locations)

Side view of standard metal-block pin termination type (LGA50D-01DADJJ) Maximum Weight = 8.8 g

(FOR METAL PINS ONLY)

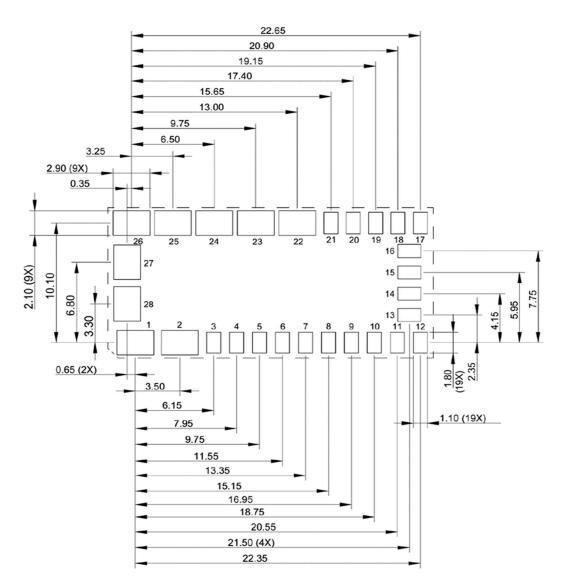

Side view of standard solder bump termination type (LGA50D-01DADJSBJ) Maximum Weight = 7.6 g

Notes: Dimensions are in millimeters Tolerance: X.XXmm±0.25mm

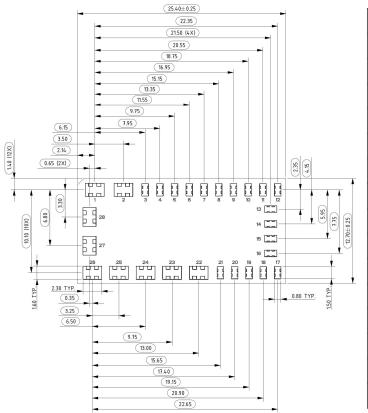

### Mechanical Drawing (Dimensioning and Mounting Locations)

#### Footprint Drawing of Metal Pins (Bottom View)

For standard metal-block pin termination (LGA50D-01DADJJ)

| Table 4. Pi | Table 4. Pin Assignments: |  |       |          |  |  |  |  |  |

|-------------|---------------------------|--|-------|----------|--|--|--|--|--|

| Pin #       | Function                  |  | Pin # | Function |  |  |  |  |  |

| 1           | Vin                       |  | 15    | CFG      |  |  |  |  |  |

| 2           | GND                       |  | 16    | Vtrim1   |  |  |  |  |  |

| 3           | PG1                       |  | 17    | VS1+     |  |  |  |  |  |

| 4           | PG2                       |  | 18    | VS1-     |  |  |  |  |  |

| 5           | EN1                       |  | 19    | Vtrim2   |  |  |  |  |  |

| 6           | EN2                       |  | 20    | VS2-     |  |  |  |  |  |

| 7           | SYNC                      |  | 21    | VS2+     |  |  |  |  |  |

| 8           | SHARE                     |  | 22    | Vol      |  |  |  |  |  |

| 9           | ADDR                      |  | 23    | Vol      |  |  |  |  |  |

| 10          | SCL                       |  | 24    | GND      |  |  |  |  |  |

| 11          | SDA                       |  | 25    | Vo2      |  |  |  |  |  |

| 12          | SALERT                    |  | 26    | Vo2      |  |  |  |  |  |

| 13          | SGND                      |  | 27    | GND      |  |  |  |  |  |

| 14          | ASCRCFG                   |  | 28    | Vin      |  |  |  |  |  |

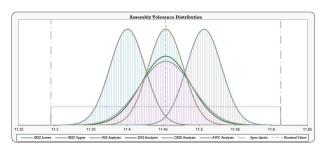

Recommended Pay Layout

Notes: Dimensions are in millimeters Tolerance: X.XXmm±0.25mm

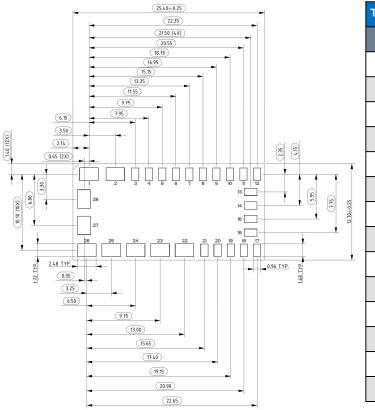

### Mechanical Drawing (Dimensioning and Mounting Locations)

#### Footprint Drawing of Solder Bumps (Bottom View)

For standard solder bump pin termination (LGA50D-01DADJSBJ)

| Table 5. Pi | Table 5. Pin Assignments: |  |       |          |  |  |  |  |  |

|-------------|---------------------------|--|-------|----------|--|--|--|--|--|

| Pin #       | Function                  |  | Pin # | Function |  |  |  |  |  |

| 1           | Vin                       |  | 15    | CFG      |  |  |  |  |  |

| 2           | GND                       |  | 16    | Vtrim1   |  |  |  |  |  |

| 3           | PG1                       |  | 17    | VS1+     |  |  |  |  |  |

| 4           | PG2                       |  | 18    | VS1-     |  |  |  |  |  |

| 5           | EN1                       |  | 19    | Vtrim2   |  |  |  |  |  |

| 6           | EN2                       |  | 20    | VS2-     |  |  |  |  |  |

| 7           | SYNC                      |  | 21    | VS2+     |  |  |  |  |  |

| 8           | SHARE                     |  | 22    | Vol      |  |  |  |  |  |

| 9           | ADDR                      |  | 23    | Vol      |  |  |  |  |  |

| 10          | SCL                       |  | 24    | GND      |  |  |  |  |  |

| 11          | SDA                       |  | 25    | Vo2      |  |  |  |  |  |

| 12          | SALERT                    |  | 26    | Vo2      |  |  |  |  |  |

| 13          | SGND                      |  | 27    | GND      |  |  |  |  |  |

| 14          | ASCRCFG                   |  | 28    | Vin      |  |  |  |  |  |

Recommended Pay Layout

Notes: Dimensions are in millimeters Tolerance: X.XXmm±0.25mm

### Mechanical Drawing (Dimensioning and Mounting Locations)

Proposed solder pad macros for standard solder bump termination (LGA50D-01DADJSBJ). It's adopted for standard metal-block pin termination (LGA50D-01DADJJ).

Recommended Pad Layout

Notes: Dimensions are in millimeters Tolerance: X.XXmm±0.25mm

Dot line represents LGA50D module outline

### Mechanical Drawing (Dimensioning and Mounting Locations)

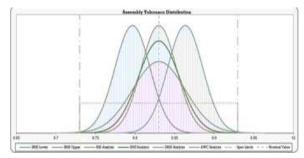

Recommended for standard metal-block-pin termination (LGA50D-01DADJJ)

Recommended Pad Layout

Notes: Dimensions are in millimeters Tolerance: X.XXmm  $\pm$  0.25mm Dot line represents LGA50D module outline

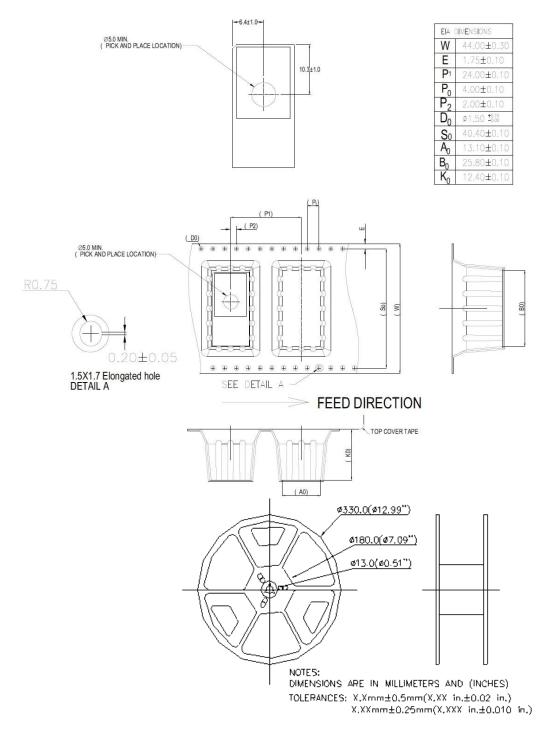

### **Mechanical Considerations**

Surface Mount Tape&Reel LGA50D-01DADJJ

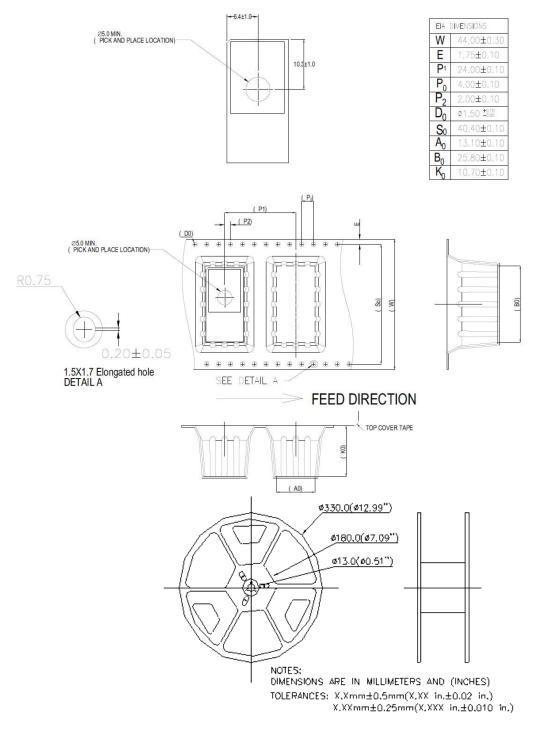

### **Mechanical Considerations**

Surface Mount Tape&Reel

### **Power and Control Signal Descriptions**

| Table 6. Pov | wer and Cont   | rol Signal D | escriptions                                                                                                                                       |

|--------------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #        | Control<br>Pin | Type1        | Function                                                                                                                                          |

| 1            | Vin            | PWR          | Input positive power pin.                                                                                                                         |

| 2            | GND            | PWR          | Power ground pin.                                                                                                                                 |

| 3            | PG1            | 0            | Vo1 power-good output. Default is push-pull, cannot be shorted to PG2.                                                                            |

| 4            | PG2            | 0            | Vo2 power-good output. Default is push-pull, cannot be shorted to PG1.                                                                            |

| 5            | EN1            |              | Enable Vo1. Active signal enables LGA50D.                                                                                                         |

| 6            | EN2            | _            | Enable Vo2. Active signal enables LGA50D.                                                                                                         |

| 7            | SYNC           | M/I/O        | Clock synchronization input. Used to set the switching frequency. Refer to Switching Frequency Setting.                                           |

| 8            | SHARE          | I/O          | Single-wire DDC bus (current sharing, LGA50Ds communication).                                                                                     |

| 9            | ADDR           | М            | Serial address select pin. Used to assign unique address for each individual device. Connect resistor to SGND. Refer to Address Setting.          |

| 10           | SCL            | I/O          | Serial clock. Connect to external host and/or to other LGA50D.Requires a pull-up resistor to a 2.5V to 5.5V source, the source must be always on. |

| 11           | SDA            | I/O          | Serial data. Connect to external host and/or to other LGA50D.Requires a pull-up resistor to a 2.5V to 5.5V source, the source must be always on.  |

| 12           | ALERT          | 0            | Serial alert. Connect to external host if desired. Requires a pull-up resistor to a 2.5V to 5.5V source, the source must be always on.            |

| 13           | SGND           | PWR          | Signal ground. SGND is shorted to GND internally on LGA50D.                                                                                       |

| 14           | ASCRCFG        | М            | Control loop configuration settings. Refer to control Loop(ASCR) Setting.                                                                         |

| 15           | CFG            | М            | Setting current sense, current limit and operating mode. Refer to Configuration Setting.                                                          |

| 16           | Vtrim1         | Μ            | Setting output voltage Vo1. Connect resistor to SGND. Refer to Output Voltage Setting.                                                            |

| 17           | VS1+           | -            | Differential output Vo1 voltage sense feedback. Connect to positive output regulation point.                                                      |

| 18           | VS1-           |              | Differential output Vo1 voltage sense feedback. Connect to negative output regulation point.                                                      |

| 19           | Vtrim2         | Μ            | Setting output voltage Vo2. Connect resistor to SGND. Refer to Output Voltage Setting.                                                            |

| 20           | VS2-           | I            | Differential output Vo2 voltage sense feedback. Connect to negative output regulation point.                                                      |

| 21           | VS2+           |              | Differential output Vo2 voltage sense feedback. Connect to positive output regulation point.                                                      |

| 22           | Vol            | PWR          | Output Vo1 positive power pin.                                                                                                                    |

| 23           | Vo1            | PWR          | Output Vo1 positive power pin.                                                                                                                    |

| 24           | GND            | PWR          | Power ground pin.                                                                                                                                 |

| 25           | Vo2            | PWR          | Output Vo2 positive power pin.                                                                                                                    |

| 26           | Vo2            | PWR          | Output Vo2 positive power pin.                                                                                                                    |

| 27           | GND            | PWR          | Power ground pin.                                                                                                                                 |

| 28           | Vin            | PWR          | Input positive power pin.                                                                                                                         |

Note 1 - I = Input, O = Output, PWR = Power or Ground, M = Multimode pins.

#### LGA50D PMBus<sup>™</sup> Interface Support

#### **PMBus™** Communications

The LGA50D provides a SMBus digital interface. The LGA50D can be used with any standard 2-wire SMBus host module. In addition, the module is compatible with SMBus version 2.0 and includes an SALRT line to help mitigate bandwidth limitations related to continuous fault monitoring. Pull-up resistors are required on the SMBus. The pull-up resistor may be tied to an external 3.3V or 5V supply as long as this voltage is present prior to or during module power-up. The ideal design will use a central pull-up resistor that is well-matched to the total load capacitance. The minimum pull-up resistance should be limited to a value that enables any module to assert the bus to a voltage that will ensure a logic 0 (typically 0.8V at the module monitoring point) given the pull-up voltage (5V if tied to VR5) and the pull-down current capability of the LGA50D (nominally 4mA). A pull-up resistor of 10Kohm is a good value for most applications.

SMBus Data and Clock lines should be routed with a closely coupled return or ground plane to minimize coupled interference (noise). Excessive noise on the data and clock lines that cause the voltage on these lines to cross the high and low logic thresholds of 2.0V and 0.8V respectively will cause command transmissions to be interrupted and result in slow bus operation or missed commands. For less than 10 modules on an SMBus a 10Kohm resistor on each line provides good performance.

The LGA50D accepts most standard PMBus<sup>™</sup> commands. When enabling the module with ON\_OFF\_CONFIG command, it is recommended that the enable pin is tied to SGND.

In addition to bus noise considerations, it is important to ensure that user connections to the SMBus are compliant to the PMBus<sup>TM</sup> command standards. Any module that can malfunction in a way that permanently shorts SMBus lines will disable PMBus<sup>TM</sup> communications. Incomplete PMBus<sup>TM</sup> commands can also cause the LGA50D to halt PMBus<sup>TM</sup> communications. This can be corrected by disabling, then re-enabling the module.

#### Monitoring via PMBus<sup>TM</sup>

A system controller can monitor a wide variety of different LGA50D parameters through the SMBus interface. The module can monitor for fault conditions by monitoring the SALRT pin, which will be asserted when any number of pre-configured fault conditions occur.

The module can also be monitored continuously for any number of power conversion parameters including but not limited to the following:

- Input voltage

- · Output voltage

- · Output current

- · Internal junction temperature

- Fault status information

The PMBus<sup>™</sup> Host should respond to SALRT as follows:

1. LGA50D module pulls SALRT Low.

2. PMBus<sup>™</sup> Host detects that SALRT is now low, performs transmission with Alert Response Address to find which LGA50D module is pulling SALRT low.

3. PMBus<sup>™</sup> Host talks to the LGA50D module that has pulled SALRT low.

The actions that the host performs are up to the System Designer.

If multiple modules are faulting, SALRT will still be low after doing the above steps and will require transmission with the Alert Response Address repeatedly until all faults are cleared.

Please refer to the PMBus<sup>™</sup> Commands section of this document for details on how to monitor specific parameters via the SMBus interface.

### LGA50D Support PMBus<sup>™</sup> Command List

| Command<br>Code | Command Name           | Default<br>Value | Access<br>Type | Data<br>Bytes | Data<br>Format | Description                                                                                    |

|-----------------|------------------------|------------------|----------------|---------------|----------------|------------------------------------------------------------------------------------------------|

| 00h             | PAGE                   | 00h              | R/W            | 1             | BIT            | Selects Controller 0, 1, or both<br>Page 0 Controller addressed                                |

| 01h             | OPERATION              | 00h              | R/W            | 1             | BIT            | Enable/disable, margin settings<br>Immediate off, nominal margin                               |

| 02h             | ON_OFF_CONFIG          | 17h              | R/W            | 1             | BIT            | On/off configuration settings<br>ENABLE pin control, active high                               |

| 03h             | CLEAR_FAULTS           | N/A              | Write          | N/A           | N/A            | Clears faults                                                                                  |

| 15h             | STORE_USER_ALL         | N/A              | Write          | N/A           | N/A            | Stores values to user store                                                                    |

| 16h             | RESTORE_USER_ALL       | N/A              | Write          | N/A           | N/A            | Restores values from user store                                                                |

| 21h             | VOUT_COMMAND           | N/A              | R/W            | N/A           | L16u           | Pin Strap Setting. Sets nominal VOUT set-point                                                 |

| 22h             | VOUT_TRIM              | 0000h            | R/W            | 2             | L16s           | Applies offset voltage to VOUT set-point                                                       |

| 23h             | VOUT_CAL_OFFSET        | 0000h            | R/W            | 2             | L16s           | Applies offset voltage to VOUT set-point                                                       |

| 24h             | VOUT_MAX               | N/A              | R/W            | N/A           | L16u           | Sets maximum VOUT set-point<br>1.15*VOUT pin strap-setting                                     |

| 25h             | VOUT_MARGIN_HIGH       | N/A              | R/W            | N/A           | L16u           | Sets VOUT set-point during margin high 1.05*VOUT pin strap -setting                            |

| 26h             | VOUT_MARGIN_LOW        | N/A              | R/W            | N/A           | L16u           | Sets VOUT set-point during margin low<br>0.95*VOUT pin strap- setting                          |

| 28h             | VOUT_DROOP             | N/A              | R/W            | N/A           | L11            | Sets V/I slope for total rail output current<br>(all phases combined)<br>CFG pin-strap setting |

| 33h             | FREQUENCY_SWITCH       | N/A              | R/W            | N/A           | L11            | Sets switching frequency<br>SYNC pin-strap setting                                             |

| 37h             | INTERLEAVE             | N/A              | R/W            | N/A           | BIT            | Configures phase offset during group<br>Operation<br>Set by pin-strapped PMBus™ address        |

| 40h             | VOUT_OV_FAULT_LIMIT    | N/A              | R/W            | N/A           | L16u           | Sets the VOUT overvoltage fault<br>Threshold. 1.1xVOUT pin-strap setting                       |

| 41h             | VOUT_OV_FAULT_RESPONSE | 80h              | R/W            | 1             | BIT            | Sets the VOUT overvoltage fault response.<br>Disable, no retry                                 |

| 44h             | VOUT_UV_FAULT_LIMIT    | N/A              | R/W            | N/A           | L16u           | Sets the VOUT under voltage fault threshold. 0.85xVOUT pin-strap setting                       |

| 45h             | VOUT_UV_FAULT_RESPONSE | 80h              | R/W            | 1             | BIT            | Sets the VOUT under voltage fault response. Disable, no retry                                  |

| 4Fh             | OT_FAULT_LIMIT         | EBE8h            | R/W            | 2             | L11            | Sets the over-temperature fault limit.<br>+125 °C                                              |

| 50h             | OT_FAULT_RESPONSE      | FFh              | R/W            | 1             | BIT            | Sets the over-temperature fault response.<br>Continuous retry, 280mS retry delay               |

| 51h             | OT_WARN_LIMIT          | EB70h            | R/W            | 2             | L11            | Sets the over-temperature warning limit.<br>+110 °C                                            |

| 55h             | VIN_OV_FAULT_LIMIT     | D3E0h            | R/W            | 2             | L11            | Sets the VIN overvoltage fault threshold.<br>15.5V                                             |

| 56h             | VIN_OV_FAULT_RESPONSE  | 80h              | R/W            | 1             | BIT            | Sets the VIN overvoltage fault response.<br>Disable, no retry                                  |

| 57h             | VIN_OV_WARN_LIMIT      | D3A0h            | R/W            | 2             | L11            | Sets the VIN overvoltage warning threshold.14.5V                                               |

| 58h             | VIN_UV_WARN_LIMIT      | CB99             | R/W            | N/A           | L11            | Sets the VIN under voltage warning<br>Threshold. 7.195V                                        |

### LGA50D Support PMBus<sup>™</sup> Command List

| Command<br>Code | Command Name          | Default<br>Value                   | Access<br>Type | Data<br>Bytes | Data<br>Format | Description                                                                               |

|-----------------|-----------------------|------------------------------------|----------------|---------------|----------------|-------------------------------------------------------------------------------------------|

| 59h             | VIN_UV_FAULT_LIMIT    | CB73                               | R/W            | N/A           | L11            | Sets the VIN under voltage fault threshold.<br>UVLO pin-strap setting. 6.898V             |

| 5Ah             | VIN_UV_FAULT_RESPONSE | BFh                                | R/W            | 1             | BIT            | Sets the VIN under voltage fault response.<br>Continuous retries, 280mS retry delay.      |

| 5Eh             | POWER_GOOD_ON         | N/A                                | R/W            | N/A           | L16u           | Sets the voltage threshold for power-<br>good Indication. 0.9 x VSET pin-strap<br>setting |

| 60h             | TON_DELAY             | D280h/<br>CA80h                    | R/W            | 2             | L11            | Sets the delay time from enable to VOUT<br>Rise.Vo1=10mS,Vo2=5mS                          |

| 61h             | TON_RISE              | CA80h                              | R/W            | 2             | L11            | Sets the rise time of VOUT after ENABLE and TON_DELAY. 5mS                                |

| 64h             | TOFF_DELAY            | CA80h                              | R/W            | 2             | L11            | Sets the delay time from DISABLE to start of VOUT fall. 5mS                               |

| 65h             | TOFF_FALL             | CA80h                              | R/W            | 2             | L11            | Sets the fall time for VOUT after DISABLE and TOFF_DELAY. 5mS                             |

| 78h             | STATUS_BYTE           | 00h                                | R              | 1             | BIT            | First byte of STATUS_WORD. No faults                                                      |

| 79h             | STATUS_WORD           | 0000h                              | R              | 2             | BIT            | Summary of critical faults. No faults                                                     |

| 7Ah             | STATUS_VOUT           | 00h                                | R              | BIT           | BIT            | Reports VOUT warnings/faults. No faults                                                   |

| 7Bh             | STATUS_IOUT           | 00h                                | R              | BIT           | BIT            | Reports IOUT warnings/faults. No faults                                                   |

| 7Ch             | STATUS_INPUT          | 00h                                | R              | BIT           | BIT            | Reports input warnings/faults. No faults                                                  |

| 7Dh             | STATUS_TEMP           | 00h                                | R              | BIT           | BIT            | Reports temperature warnings/faults. No faults                                            |

| 7Eh             | STATUS_CML            | 00h                                | R              | BIT           | BIT            | Reports communication, memory, logic<br>Errors. No faults                                 |

| 80h             | STATUS_MFR_SPECIFIC   | 00h                                | R              | BIT           | BIT            | Reports voltage monitoring/clock<br>synchronization faults. No faults                     |

| 88h             | READ_VIN              | N/A                                | R              | N/A           | L11            | Reports input voltage measurement                                                         |

| 8Bh             | READ_VOUT             | N/A                                | R              | N/A           | L16u           | Reports output voltage measurement                                                        |

| 8Ch             | READ_IOUT             | N/A                                | R              | N/A           | L11            | Reports output current measurement                                                        |

| 8Dh             | READ_TEMPERATURE_1    | N/A                                | R              | L11           | N/A            | Reports internal temperature<br>measurement                                               |

| 8Fh             | READ_TEMPERATURE_3    | N/A                                | R              | L11           | N/A            | Reports external temperature<br>measurement from Mosfet pin                               |

| 94h             | READ_DUTY_CYCLE       | N/A                                | R              |               | L11            | Reports actual duty cycle                                                                 |

| 95h             | READ_FREQUENCY        | N/A                                | R              |               | L11            | Reports actual switching frequency                                                        |

| 98h             | PMBus™_REVISION       | 22h                                | R              | 1             | BIT            | Reports the PMBus™ revision used                                                          |

| 99h             | MFR_ID                | N/A                                | R/W            |               | ASC            | LGA50D-01DADJJ/LGA50D-<br>01DADJSBJ                                                       |

| 9Bh             | MFR_REVISION          | JJ =<br>303034<br>JSBJ =<br>303032 | R/W            |               | ASC            | Sets a user defined revision.JJ = 004,<br>JSBJ = 002                                      |

| 9Ch             | MFR_LOCATION          | N/A                                | R/W            |               | ASC            | Sets a user defined location identifier                                                   |

| 9Dh             | MFR_DATE              | N/A                                | R/W            |               | ASC            | Sets a user defined date                                                                  |

| 9Eh             | MFR_SERIAL            | N/A                                | R/W            |               | ASC            | Serial number                                                                             |

| B0h             | USER_DATA_00          | N/A                                | R/W            |               | ASC            | Sets user defined data                                                                    |

| D1h             | USER_CONFIG           | N/A                                | R/W            |               | BIT            | Configures several user-level features<br>Set by CFG pin-strap setting                    |

advancedenergy.com 29

### LGA50D Support PMBus<sup>™</sup> Command List

| Command<br>Code | Command Name                   | Default<br>Value | Access<br>Type | Data<br>Bytes | Data<br>Format | Description                                                                                                                          |

|-----------------|--------------------------------|------------------|----------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| D3h             | DDC_CONFIG                     | N/A              | R/W            |               | BIT            | Configures the DDC addressing and<br>current sharing. Set by pin-strapped<br>PMBus <sup>™</sup> address and CFG pin-strap<br>setting |

| D4h             | POWER_GOOD_DELAY               | BA00h            | R/W            | 2             | L11            | Sets the delay between PG threshold and PG assertion                                                                                 |

| D5h             | MULTI_PHASE_RAMP_GAIN          | 03h              | R/W            | 1             | CUS            | Adjusts the ramp-up and ramp-down rate by setting the feedback gain                                                                  |

| D7h             | SNAPSHOT_FAULT_MASK            | 00h              | R/W            | 1             | 00h            | Masks faults that cause a snapshot to be<br>Taken. No faults masked                                                                  |

| DBh             | MFR_SMBALERT_MASK              | 00h              | R/W            | 1             | Custom         | Identifies which fault limits will not assert SALRT                                                                                  |

| DDh             | PINSTRAP_READ_STATUS           | N/A              | Read           |               | BIT            | Set by pin-straps                                                                                                                    |

| DFh             | ASCR_CONFIG                    | N/A              | R/W            |               | BIT            | Configures the ASCR settings<br>ASCRCFG pin-strap setting                                                                            |

| E0h             | SEQUENCE                       | 00h              | R/W            |               | BIT            | DDC rail sequencing configuration<br>Prequel and sequel disabled                                                                     |

| E2h             | DDC_GROUP                      | N/A              | Block<br>R/W   |               | BIT            | Configures group ID, fault spreading,<br>OPERATION and VOUT<br>Set by CFG pin-strap                                                  |

| E5h             | MFR_IOUT_OC_FAULT_RESPO<br>NSE | 80h              | R/W            | 1             | BIT            | Configures the IOUT over current fault<br>Response Disable, no retry                                                                 |

| E6h             | MFR_IOUT_UC_FAULT_RESPO<br>NSE | 80h              | R/W            | 1             | BIT            | Configures the IOUT undercurrent fault<br>Response Disable, no retry                                                                 |

| E7h             | IOUT_AVG_OC_FAULT_LIMIT        | N/A              | R/W            | L11           | L11            | Sets the IOUT average over current fault<br>Threshold. Set by CFG pin-strap                                                          |

| E9h             | USER_GLOBAL_CONFIG             | N/A              | R/W            |               | BIT            | Sets options pertaining to advanced<br>Feature. Set by CFG pin-strap setting                                                         |

| EAh             | SNAPSHOT                       | N/A              | Read           |               | BIT            | 32-byte read-back of parametric and status values                                                                                    |

| F0h             | LEGACY_FAULT_GROUP             | 0000000<br>0h    | R/W            |               | BIT            | Configures fault group compatibility with older digital power devices                                                                |

| F3h             | SNAPSHOT_CONTROL               | 00h              | R/W            | 1             | BIT            | Snapshot feature control command                                                                                                     |

| F4h             | RESTORE_FACTORY                | N/A              | Write          | N/A           | N/A            | Restores device to the hard-coded default values                                                                                     |

| F5h             | MFR_VMON_OV_FAULT_LIMIT        | C266h            | R/W            | 2             | L11            | Sets the VMON overvoltage fault<br>threshold<br>2.4V, SPS OT trip voltage                                                            |

| F6h             | MFR_VMON_UV_FAULT_LIMIT        | 9B33h            | R/W            | 2             | L11            | Sets the VMON under voltage fault<br>Threshold.0.1V, corresponds to -50 °C                                                           |

| F7h             | MFR_READ_VMON                  | N/A              | Read           |               | L11            | Reads the VMON voltage                                                                                                               |

| F8h             | VMON_OV_FAULT_RESPONSE         | BFh              | R/W            | 1             | BIT            | Configures the VMON overvoltage fault<br>Response Continuous retry                                                                   |

| F9h             | VMON_UV_FAULT_RESPONSE         | BFh              | R/W            | 1             | BIT            | Configures the VMON under voltage fault Response. Continuous retry                                                                   |

| FAh             | SECURITY_LEVEL                 | 01H              | Read           | 1             | Hex            | Reports the security level<br>Public security level                                                                                  |

| FBh             | PRIVATE_PASSWORD               | 0000h            | R/W            |               | ASC            | Sets the private password string                                                                                                     |

| FCh             | PUBLIC_PASSWORD                | 0000h            | R/W            |               | ASC            | Sets the public password string                                                                                                      |

### PMBus<sup>™</sup> Use Guidelines

The PMBus<sup>™</sup> is a powerful tool that allows the user to optimize circuit performance by configuring the LGA50D for their application. When configuring the LGA50D, the LGA50D should be disabled whenever most settings are changed with PMBus commands. Some exceptions to this recommendation are OPERATION, ON\_OFF\_CONFIG, CLEAR\_FAULTS, VOUT\_COMMAND, VOUT\_MARGIN\_HIGH, VOUT\_MARGIN\_LOW and ASCCR\_CONFIG. While the LGA50D is enabled any command can be read. Many commands do not take effect until after the LGA50D has been re-enabled, hence the recommendation that commands that change device settings are written while the LGA50D is disabled. When sending the STORE\_DEFAULT\_ALL, STORE\_USER\_ALL, RESTORE\_DEFAULT\_ALL and RESTORE\_USER\_ALL commands, it is recommended that no other commands are sent to the device for 100mS after sending STORE or RESTORE commands. In addition, there should be a 2mS delay between repeated READ commands sent to the same device. When sending any other command, a 5mS delay is recommended between repeated commands sent to the same device.

#### SUMMARY

All commands can be read at any time.

Always disable the LGA50D when writing commands that change device settings. Exceptions to this rule are commands intended to be written while the LGA50D is enabled, for example, VOUT\_MARGIN\_HIGH.

To be sure a change to LGA50D setting has taken effect, write the STORE\_USER\_ALL command, then cycle input power and reenable the LGA50D.

### PMBus<sup>™</sup> Data Formats

#### Linear-11 (L11)

L11 data format uses 5-bit two's compliment exponent (N) and 11-bit two's compliment mantissa (Y) to represent real world decimal. value (X).

| Data Byte High      | Data Byte Low |  |  |  |  |  |

|---------------------|---------------|--|--|--|--|--|

| 76543210            | 76543210      |  |  |  |  |  |

| $\smile \checkmark$ |               |  |  |  |  |  |

Exponent (N) Mantissa (Y)

Relation between real world decimal value (X), N and Y is: =  $Y \cdot 2^{N}$ .

#### Linear-16 Unsigned (L16u)

L16u data format uses a fixed exponent (hard-coded to N = -13h) and a 16-bit unsigned integer mantissa (Y) to represent real world decimal value (X). Relation between real world decimal value (X), N and Y is:  $X = Y \cdot 2^{-13}$ .

#### Linear-16 Signed (L16s)

L16s data format uses a fixed exponent (hard-coded to N = -13h) and a 16-bit two's compliment mantissa (Y) to represent real world decimal value (X). Relation between real world decimal value (X), N and Y is:  $X = Y \cdot 2^{-13}$ .

#### **Bit Field (BIT)**

Breakdown of Bit Field is provided in "PMBus™ Command Detail" starting on page 33.

#### Custom (CUS)

Breakdown of Custom data format is provided in "PMBus™ Command Detail". A combination of Bit Field and integer are common type of Custom data format.

#### ASCII (ASC)

A variable length string of text characters uses ASCII data format.

#### Block R/W type

If command type is Block R/W, please add one bit at the beginning defined data length in bytes.

### PMBus<sup>™</sup> Command Detail

### PAGE (00h)

**Definition**: Selects phase1(page 01), phase2(page 00) or both phase1 and 2 to receive commands. All commands following this command will be received and acted on by the selected controller or controllers.

Data Length in Bytes: 1

Data Format: Bit Field

Type: R/W

Protectable: No

Default Value: 00h (Page 0)

Units: N/A

| COMMAND       | PAGE (00h)          |           |     |     |     |     |     |     |

|---------------|---------------------|-----------|-----|-----|-----|-----|-----|-----|

| Format        |                     | Bit Field |     |     |     |     |     |     |

| Bit Position  | 7                   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

| Access        | R/W                 | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |

| Function      | See Following Table |           |     |     |     |     |     |     |

| Default Value | 0                   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT 7:4 | BIT 3:0 | PAGE |

|---------|---------|------|

| 0000    | 0000    | 0    |

| 0000    | 0001    | 1    |

| 1111    | 1111    | Both |

### **OPERATION** (01h)

**Definition**: Sets Enable, Disable and VOUT Margin settings. This command can also be monitored to read the operating state of the device on bits 7:6. Writing Immediate off will turn off the output and ignore TOFF\_DELAY and TOFF\_FALL settings. This command is not stored like other PMBus<sup>TM</sup> commands. The value read reflects the current state of the device. When this command is written the command takes effect, but if a STORE \_USER\_ALL written and the device is re-enabled, the OPERATION settings may not be the same settings that were written before the device was re-enabled.

Paged or Global: Paged

Data Length in Bytes: 1

Data Format: Bit Field

Type: R/W

Protectable: Yes

Default Value: 00h (immediate off)

Units: N/A

| COMMAND                      | OPERATION (01h) |            |     |     |     |     |     |     |

|------------------------------|-----------------|------------|-----|-----|-----|-----|-----|-----|

| Format                       |                 | Bit Field  |     |     |     |     |     |     |

| Bit Position                 | 7               | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

| Access                       | R/W             | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Function See Following Table |                 | ving Table |     |     |     |     |     |     |

| Default Value                | 0               | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT 7:6 | BIT 5:4 | BIT 3:0<br>(NOT USED) | UNIT ON OR OFF                   | MARGIN STATE |

|---------|---------|-----------------------|----------------------------------|--------------|

| 00      | 00      | 0000                  | Immediate off (No<br>sequencing) | N/A          |

| 01      | 00      | 0000                  | Soft off (With sequencing)       | N/A          |

| 10      | 00      | 0000                  | On                               | Nominal      |

| 10      | 01      | 0000                  | On                               | Margin Low   |

| 10      | 10      | 0000                  | On                               | Margin High  |

Note: Bit combinations not listed above may cause command errors.

### $\mathsf{ON\_OFF\_CONFIG}\left(\mathsf{02h}\right)$

**Definition**: Configures the interpretation and coordination of the OPERATION command and the ENABLE pin (EN). When bit 0 is set to 1(turn off the output immediately), the TOFF\_FALL setting is ignored.

Paged or Global: Paged

Data Length in Bytes: 1

Data Format: Bit Field

Type: R/W

Protectable: Yes

Default Value: 17h (ENABLE pin control, active high, turn off output immediately – no ramp down)

#### Units: N/A

| COMMAND       | ON_OFF_CONFIG (02h) |     |     |     |     |     |     |     |

|---------------|---------------------|-----|-----|-----|-----|-----|-----|-----|

| Format        | Bit Field           |     |     |     |     |     |     |     |

| Bit Position  | 7                   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Access        | R/W                 | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function      | See Following Table |     |     |     |     |     |     |     |

| Default Value | 0                   | 0   | 0   | 1   | 0   | 1   | 1   | 1   |

| BIT NUMBER | PURPOSE                                                                           | BIT VALUE | DESCRIPTION                                        |

|------------|-----------------------------------------------------------------------------------|-----------|----------------------------------------------------|

| 7:5        | Not Used                                                                          | 000       | Not used                                           |

|            | Sets the default to either operate any time                                       | 000       | Not used                                           |

| 4:2        | power is present or for the on/off to be<br>controlled by ENABLE pin or OPERATION | 101       | Device starts from ENABLE pin only.                |

|            | command                                                                           | 110       | Device starts from OPERATION command only.         |

| 1          | (Polarity of ENABLE pin - not used)                                               | 1         | Active high only.                                  |

| 0          | ENABLE pin action when commanding                                                 | 0         | Use the configured ramp-down settings ("soft-off") |

| 0          | the unit to turn off                                                              | 1         | Turn off the output immediately.                   |

### LGA50D Series

## PMBus<sup>™</sup> SPECIFICATIONS

#### CLEAR\_FAULTS (03h)

**Definition**: Clears all fault bits in all registers and releases the SALRT pin (if asserted) simultaneously. If a fault condition still exists, the bit will reassert immediately. This command will not restart a device if it has shut down, it will only clear the faults.

Paged or Global: Global

Data Length in Bytes: 0 Byte

Data Format: N/A

Type: Write only

Protectable: Yes

Default Value: N/A

Units: N/A

#### STORE\_USER\_ALL (15h)

**Definition**: Stores all PMBus<sup>™</sup> settings from the operating memory to the nonvolatile USER store memory. To clear the USER store, perform a RESTORE\_FACTORY then STORE\_USER\_ALL. To add to the USER store, perform a RESTORE\_USER\_ALL, write commands to be added, then STORE\_USER\_ALL. This command should not be used during device operation, the device will be unresponsive for 100mS while storing values.

Paged or Global: Global

Data Length in Bytes: 0

Data Format: N/A

Type: Write only

Default Value: N/A

Units: N/A

#### RESTORE\_USER\_ALL (16h)

**Definition**: Restores all PMBus<sup>™</sup> settings from the USER store memory to the operating memory. Command performed at powerup. Security level is changed to Level 1 following this command. This command should not be used during device operation, the device will be unresponsive for 100mS while restoring values.

Paged or Global: Global

Data Length in Bytes: 0

Data Format: N/A

Type: Write only

Default Value: N/A

Units: N/A

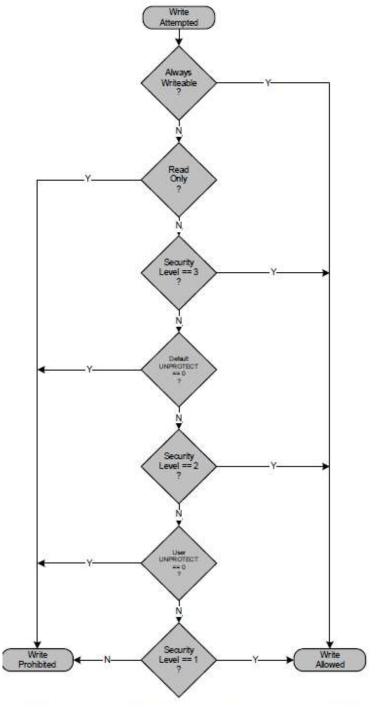

#### VOUT\_COMMAND (21h)